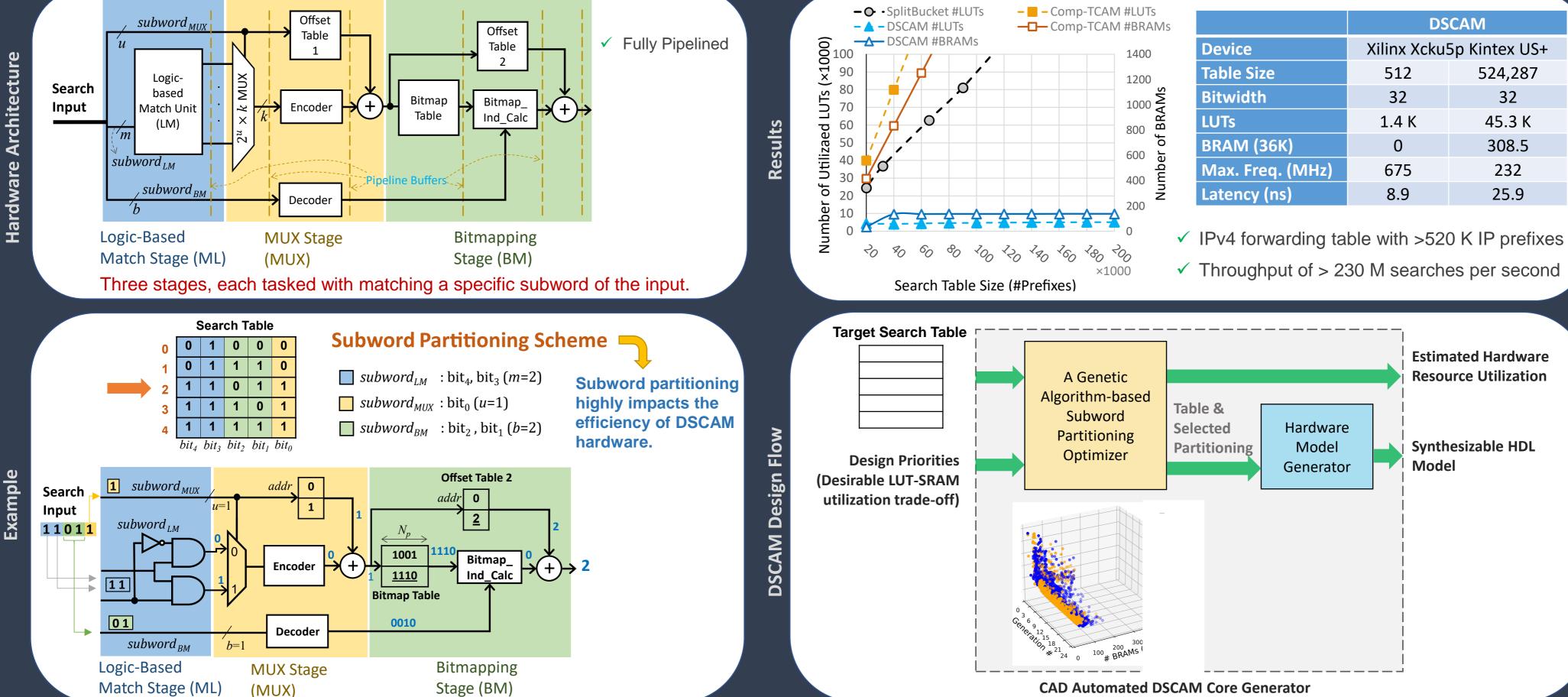

## DSCAM: Latency-Guaranteed and High-Capacity Content Addressable Memory on FPGAs

- An innovative approach to implement content-addressable memory on FPGA High-throughput, short and fixed latency

- Cost-effective: enables implementing large search tables on budget-friendly FPGAs

- Adjustable trade-off between logic resource and SRAM utilization based on the design priorities

Institut national de la recherche scientifique

ECCoLe Edge Computing, Communication and Learning Lab

|                  | DSCAM                    |         |

|------------------|--------------------------|---------|

| Device           | Xilinx Xcku5p Kintex US+ |         |

| Table Size       | 512                      | 524,287 |

| Bitwidth         | 32                       | 32      |

| LUTs             | 1.4 K                    | 45.3 K  |

| BRAM (36K)       | 0                        | 308.5   |

| Max. Freq. (MHz) | 675                      | 232     |

| Latency (ns)     | 8.9                      | 25.9    |