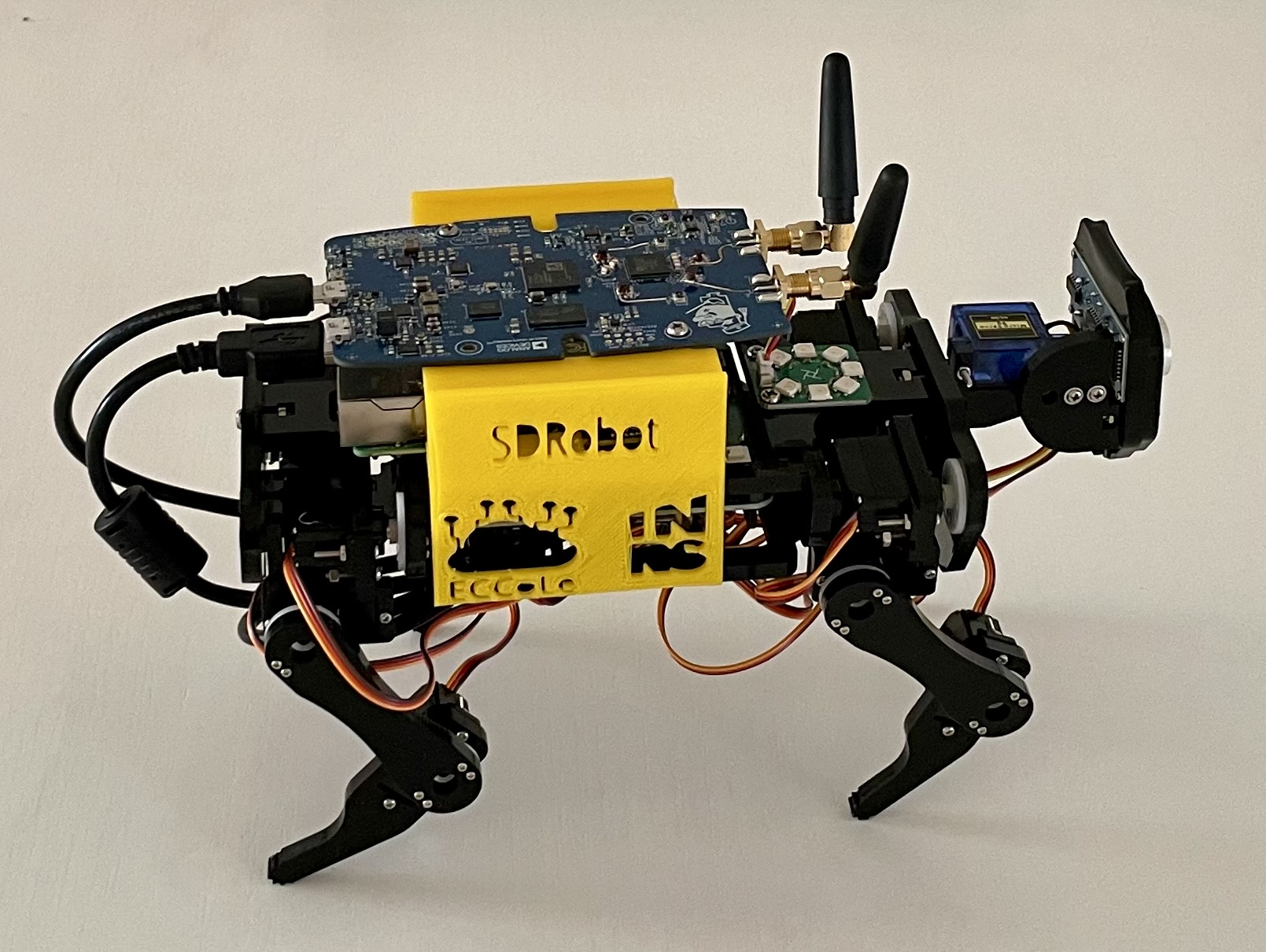

SDRobot_v1

SDRobot (Software-defined Radio Robot)-v1 is the first version of SDR-enabled robots, developed at the ECCoLe lab for prototyping and evaluating machine learning-assisted wireless signal processing techniques, including collaborative solutions.

SDRobot-v1 is equipped with an Analog Devices ADALM-PLUTO SDR, a Raspberry Pi 4B, and a Google Edge TPU.

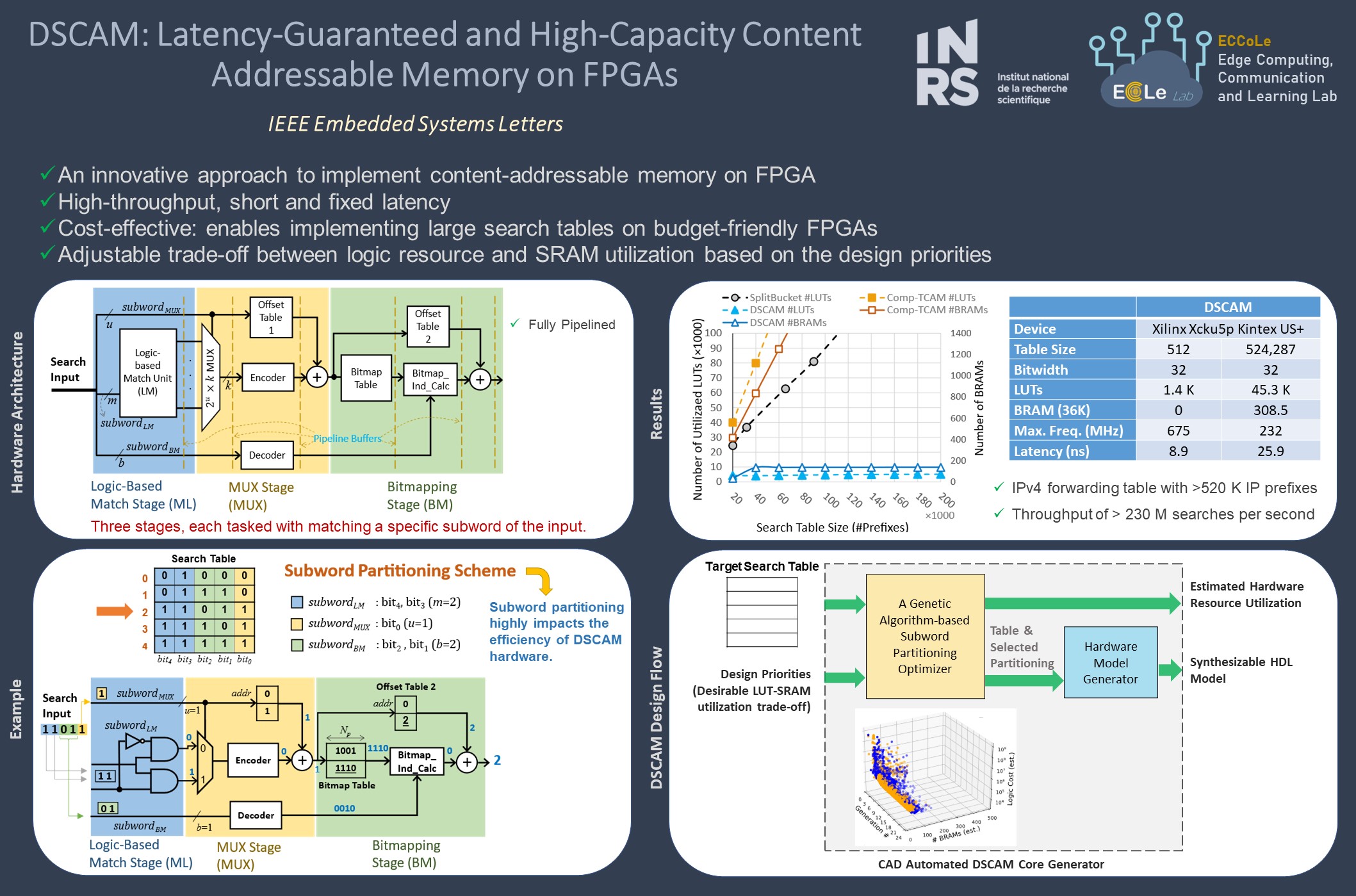

DSCAM/DSCAM+

DSCAM (Directly Synthesized Content-Addressable Memory) is an innovative approach to implement large content-addressable memories (CAMs) and ternary CAMs (TCAMs) on budget-friendly FPGAs,

delivering fixed latency and high-throughput search capabilities. A CAD framework has been developed to automatically generate content-specific DSCAM hardware cores,

utilizing a genetic algorithm-based optimizer. Leveraging the inherent flexibility of FPGAs, rapid search speeds, and support for large search tables,

DSCAM emerges as a highly promising solution for replacing TCAMs in SDN-enabled data planes.

In a practical test scenario, DSCAM demonstrated its capabilities by effectively implementing a real-world IPv4 forwarding table containing more than 520 K prefixes

on an xcku5p AMD/XILINX Kintex UltraScale+ FPGA. This accomplishment was marked by an impressively low lookup latency of under 29 nanoseconds and

an impressive throughput of 215 million lookups per second.

DSCAM+ is an extension that makes slight enhancements to the hardware microarchitecture while introducing a fast heuristic algorithm as an alternative to

the Genetic Algorithm for optimization tasks. DSCAM is available open source:

https://github.com/INRS-ECCoLe/DSCAM

High quality graphic abstract in pdf

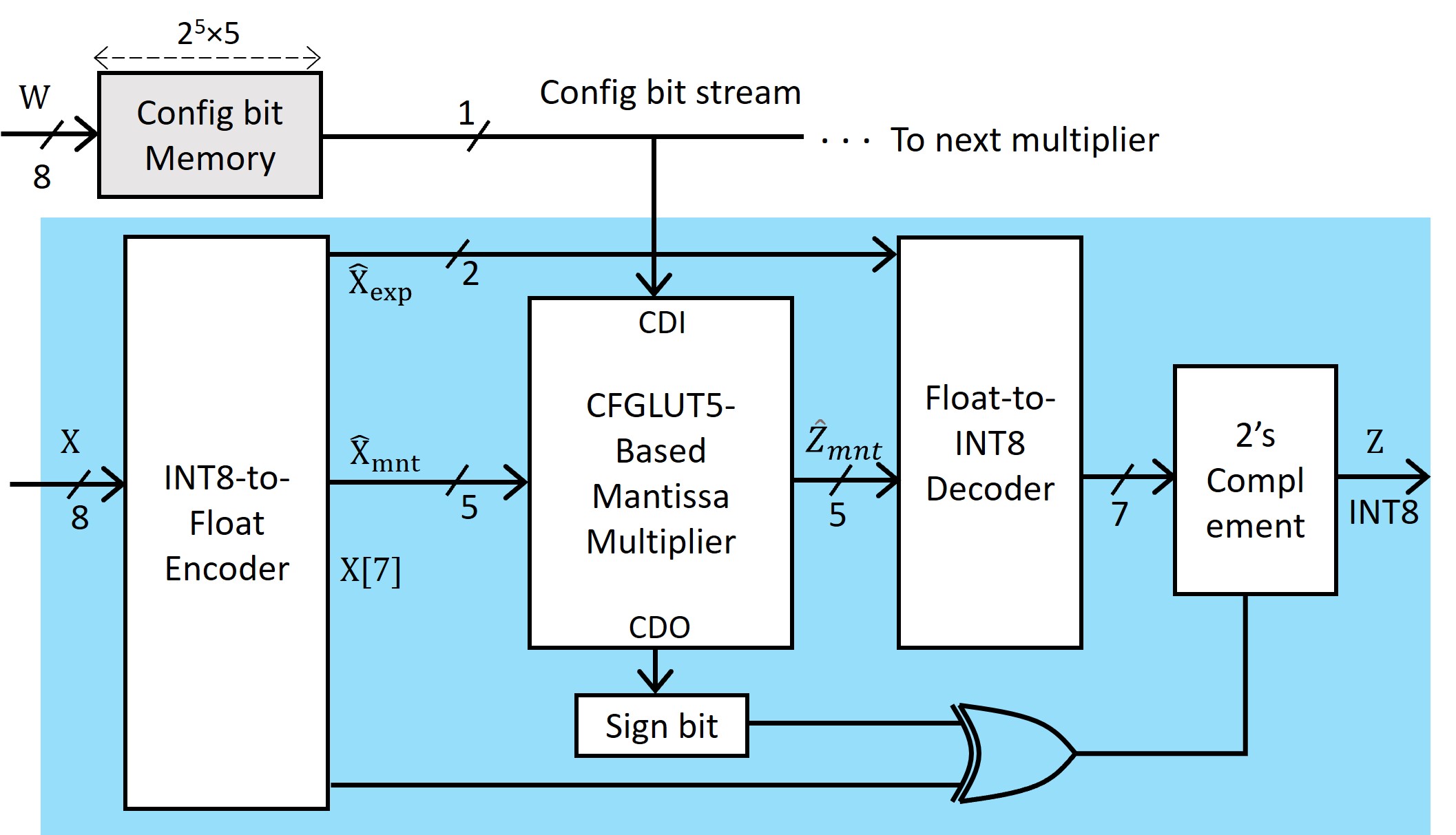

DyRecMul

DyRecMul (Dynamically Reconfigurable approximate Multiplier) is a novel FPGA-based approximate multiplier tailored for machine learning computations.

Leveraging dynamically reconfigurable lookup table (LUT) primitives within AMD-Xilinx technology, it effectively executes the essential computations at its core.

Evaluation on an AMD-Xilinx Kintex Ultrascale+ FPGA showcases substantial efficiency gains, with a noteworthy reduction of 64% and 67% in LUT utilization observed for signed multiplication and multiply-and-accumulate configurations, respectively, when compared to the conventional Xilinx multiplier core.

Accuracy evaluations conducted across various benchmark deep learning models reveal minimal degradation, demonstrating the resilience of DyRecMul even during post-training inference.

DyRecMul is available open source: https://github.com/INRS-ECCoLe/DyRecMul

More detail can be found in our preprint paper: https://arxiv.org/abs/2310.10053

HENNC

HENNC (Hardware Engine for Artificial Neural Network-Based Chaotic Oscillators) is a computer-aided design framework that, for the first time, automates the creation of efficient hardware architectures for ANN-based chaotic oscillators on FPGAs.

Users input ANN hyperparameters, and HENNC generates a list of Pareto-optimal candidate architectures, each offering a distinct tradeoff between throughput and hardware cost.

The framework then produces the corresponding High-Level Synthesis (HLS) model of the selected candidate, using HLS directives to define trade-offs between hardware cost and latency.

HENNC employs innovative latency and hardware cost estimation functions to expedite the design space exploration process.

HENNC is available open source: https://github.com/INRS-ECCoLe/HENNC